从芯片到系统 半导体封装技术演进路线图及其对计算机软硬件技术开发的深刻影响

半导体封装技术,作为连接芯片内部微观世界与外部宏观应用的桥梁,其演进历程深刻塑造了计算技术的格局。从最初的保护性外壳到如今的高性能、高集成度系统级载体,封装技术的每一次革新都成为驱动计算机软硬件技术开发的关键力量。本文将勾勒半导体封装技术的演进路线图,并深入探讨其对软硬件开发的连锁影响。

一、半导体封装技术的演进路线图

1. 传统封装时代(1970s-1990s):从通孔插装到表面贴装

- 双列直插封装(DIP):早期主流,通过引脚插入印刷电路板(PCB)的孔中实现连接。特点是结构简单、成本低,但集成度低、占用面积大,限制了早期个人电脑和微处理器的性能与体积。

- 小外形封装(SOP)、四方扁平封装(QFP):随着表面贴装技术(SMT)兴起,这些封装形式将引脚分布在封装体四周或底部,直接焊接在PCB表面。这显著提高了PCB的组装密度和可靠性,为更紧凑的硬件设计(如笔记本电脑、便携设备)奠定了基础。

2. 先进封装崛起时代(1990s-2010s):追求高密度与高性能

- 球栅阵列封装(BGA):用位于封装底部的焊球阵列代替周边引脚,极大地增加了I/O数量,缩短了信号路径,提升了电气性能和散热能力。BGA成为CPU、GPU、芯片组等高性能芯片的标准封装,直接推动了处理器频率和功能的飞跃。

- 芯片级封装(CSP):封装尺寸接近芯片本身,实现了极致的微型化,广泛应用于移动设备(如智能手机)中的存储器、传感器等,是移动计算硬件小型化的核心推手。

- 多芯片模块(MCM)与系统级封装(SiP):将多个不同功能的裸芯片(如逻辑、存储、模拟)集成在一个封装内。这实现了功能的异构集成,减少了互连延迟和系统体积,在通信设备、可穿戴设备中早期应用,预示了系统集成的未来方向。

3. 异构集成与“超越摩尔”时代(2010s-至今):走向系统级创新

- 扇出型封装(Fan-Out):如台积电的InFO技术,允许在芯片外部区域重新布线并放置I/O焊球,实现了更薄的封装、更高的I/O密度和更好的散热。这使手机应用处理器能集成更多功能并与内存更紧密耦合。

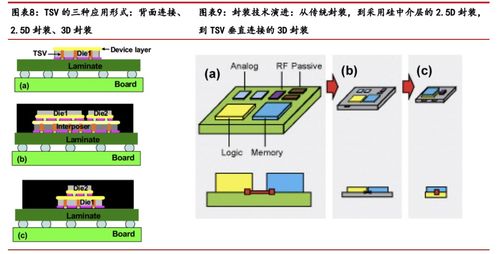

- 2.5D/3D封装:

- 2.5D封装:使用硅中介层(Interposer)将多个芯片并排连接在同一基板上,通过中介层中的高密度互连(如硅通孔TSV)实现芯片间的高速通信。典型代表是CoWoS(Chip on Wafer on Substrate),用于高端GPU、AI加速器,实现了海量数据的高带宽传输。

- 3D封装:将芯片在垂直方向上堆叠并通过TSV直接互连,极大缩短了互连长度,实现了前所未有的带宽和能效。如HBM(高带宽内存)与处理器的3D堆叠,解决了“内存墙”瓶颈,对高性能计算和人工智能至关重要。

- 芯粒(Chiplet)与先进互连:将大型SoC分解为多个较小、功能模块化的芯粒,通过先进封装(如Intel的EMIB、AMD的Infinity Fabric)进行异构集成。这降低了大规模芯片的制造成本和设计复杂度,并允许混合使用不同工艺节点的芯粒,成为延续摩尔定律经济效益的关键路径。

二、对计算机软硬件技术开发的深刻影响

对硬件开发的影响:

- 性能突破:先进封装通过缩短互连距离、增加带宽,直接提升了处理器与内存之间的数据吞吐量,缓解了性能瓶颈。例如,3D堆叠的HBM使得AI训练和科学计算的硬件效率成倍提升。

- 形态革新:封装小型化使设备更轻薄(如超极本、折叠屏手机),而SiP和异构集成则催生了高度集成、功能丰富的硬件模块(如系统模块SoM),加速了物联网终端、边缘计算设备的创新。

- 设计范式转变:芯粒架构催生了新的硬件设计模式。硬件开发者可以像“搭积木”一样,选用不同供应商或工艺的预制芯粒,专注于系统架构和集成,从而加快产品上市时间,降低高端芯片的开发风险和成本。

- 散热与功耗挑战:高密度集成带来了更高的功率密度,对散热解决方案(如均热板、液体冷却)提出了极致要求,同时也推动了硬件层面的功耗精细管理技术发展。

对软件开发的影响:

- 系统架构抽象层变化:对于采用3D堆叠、芯粒架构的硬件,操作系统和底层驱动需要能够识别和管理这些在物理上紧密耦合但逻辑上可能独立的计算单元、内存层次和互连拓扑。这可能需要新的硬件抽象层和资源管理模型。

- 并行与异构编程模型深化:为了充分发挥由先进封装集成带来的多核、众核以及CPU、GPU、AI加速器、高速内存的协同计算能力,软件并行编程模型(如OpenMP、CUDA)和异构计算框架(如SYCL、oneAPI)需要不断演进,以更高效地调度和利用这些紧密集成的硬件资源。

- 内存与存储层级优化:封装内集成的超高速内存(如HBM)与较慢的系统主存、存储构成了更复杂的内存层级。数据库、大数据分析、科学计算等软件需要优化数据放置和访问策略,以匹配新的硬件内存特性,最大化性能收益。

- 安全与可靠性考量:复杂的异构集成系统可能引入新的安全边界和故障点。软件,特别是固件、虚拟化管理程序和安全模块,需要适应这种新的物理形态,确保系统安全和可靠运行。

###

半导体封装技术的演进,已经从单纯的“保护与连接”,演变为决定系统性能、形态和成本的核心设计维度。其路线图清晰地指向更高密度、更高带宽、更异构集成的未来。对于计算机软硬件开发者而言,理解并顺应这一趋势至关重要。硬件开发者需拥抱芯粒化和异构集成设计,软件开发者则需为其打造的高效、复杂的计算系统编写更智能、更能发挥硬件潜力的代码。封装与软硬件的协同创新,正共同绘制着下一代计算系统的宏伟蓝图。

如若转载,请注明出处:http://www.songshu777.com/product/77.html

更新时间:2026-04-14 14:45:41