集成电路技术驱动下的平板相控阵天线设计与计算机软硬件协同开发

随着无线通信、雷达探测等领域的飞速发展,对天线系统的性能要求日益提高。传统机械扫描天线在响应速度、可靠性及多功能集成方面面临瓶颈。在此背景下,集成电路(IC)技术的持续突破,正成为推动平板相控阵天线设计迈向高性能、小型化、低成本的关键引擎,并与计算机软硬件技术开发深度融合,共同塑造新一代智能天线系统。

一、 IC集成技术:平板相控阵天线的核心驱动力

平板相控阵天线的核心在于通过大量规则排列的辐射单元及其配套的移相器、功分网络等组件,实现波束的电子扫描与赋形。其性能优势(如敏捷波束、多波束、高增益)的实现,高度依赖于底层射频前端、控制与处理电路的集成度与性能。

- 硅基与化合物半导体工艺的演进:基于硅(Si CMOS、SiGe)和化合物半导体(GaAs、GaN)的先进IC工艺,使得在毫米波甚至更高频段实现高性能、低功耗的发射/接收(T/R)模块成为可能。单片微波集成电路(MMIC)技术将功率放大器、低噪声放大器、移相器、衰减器等关键功能集成于单一芯片,极大地减小了模块体积和重量,提升了可靠性与生产效率,为在有限平板空间内密集排布上千甚至上万个单元奠定了基础。

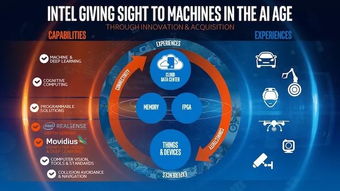

- 数字与模拟混合信号集成:现代相控阵天线正朝着数字化方向发展。数字波束成形(DBF)技术通过在单元级或子阵级集成模数/数模转换器(ADC/DAC),将射频信号直接在数字域进行处理。这要求高度集成的数字控制与信号处理IC,能够实现更灵活的波束控制、更强的抗干扰能力和更便捷的多功能集成(如通信雷达一体化)。

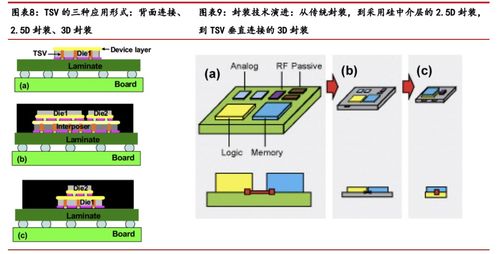

- 封装与集成技术的创新:系统级封装(SiP)、晶圆级封装(WLP)、天线封装(AiP)等先进封装技术,允许将射频芯片、数字控制芯片、无源元件乃至天线辐射结构进行三维异构集成。这不仅进一步压缩了系统体积,缩短了互连路径、降低了损耗,还为实现更高频率、更宽带性能的平板天线提供了技术路径。

二、 计算机软硬件技术的协同开发与赋能

IC集成为硬件平台提供了强大的“躯干”,而计算机软硬件技术则构成了其智能化的“大脑”与“神经网络”,两者协同工作,共同释放平板相控阵天线的全部潜能。

- 硬件层面的协同:

- 高速数字处理平台:现场可编程门阵列(FPGA)和专用集成电路(ASIC)为实时波束成形、信号处理与自适应算法提供了强大的并行计算能力。高性能FPGA允许算法快速迭代与功能重构,而针对特定应用优化的ASIC则能实现极致的能效比与处理速度。

- 高速互连与数据交换:大规模阵列产生的海量数据对背板与板间互连技术提出了极高要求。高速串行接口(如SerDes)、光互连等技术,确保了控制指令与数据流在系统内部的高速、可靠传输。

- 软件与算法层面的核心作用:

- 设计与仿真工具链:基于电磁场仿真、电路仿真和系统级仿真的EDA(电子设计自动化)软件,是天线设计、阵列布局优化、IC-天线协同仿真的关键。高性能计算(HPC)集群的运用,使得对包含成千上万个单元的复杂系统进行精确仿真成为可能,大幅缩短了设计周期。

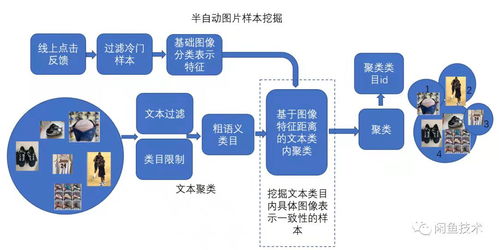

- 控制与信号处理算法:波束指向控制、自适应波束成形、空时信号处理、校准与自愈等先进算法,是相控阵天线发挥其智能特性的灵魂。这些算法的开发、验证与实时实现,依赖于高效的软件编程模型(如OpenCL、HDL Coder)和算法库。

- 系统控制与管理软件:负责资源调度、任务管理、状态监控、故障诊断的上层应用软件,使得相控阵天线能够灵活适应复杂的任务场景,并实现智能化运维。

三、 未来趋势与挑战

IC集成与计算机软硬件技术的融合,正推动平板相控阵天线向更高频段(太赫兹)、更大规模、更智能化、更低成本(消费级应用,如5G/6G、卫星互联网终端、车载雷达)方向发展。也面临诸多挑战:

- 热管理与功耗:高集成度带来的功率密度增加,对高效散热设计提出严峻考验。

- 校准与测试复杂度:大规模阵列的快速、精准校准与测试需要创新的自动化方案。

- 异构集成与协同设计:如何更高效地进行从IC、封装、天线到系统软件的跨层级、跨领域协同设计与优化,是提升整体性能的关键。

- 安全与可靠性:在软件定义一切的趋势下,系统的网络安全与功能安全至关重要。

结论

集成电路技术是平板相控阵天线实现其物理形态与基础功能的核心基石,而计算机软硬件技术则是赋予其灵活性、智能化与可扩展性的关键使能因素。两者的深度融合与协同创新,不仅推动了天线技术的革命性进步,更在通信、感知、电子战等多个领域催生出前所未有的应用可能。随着工艺节点的持续微缩、异构计算架构的演进以及人工智能算法的深度嵌入,平板相控阵天线将变得更加强大、智能和普及,成为连接物理世界与数字世界的重要桥梁。

如若转载,请注明出处:http://www.songshu777.com/product/66.html

更新时间:2026-04-14 16:54:59